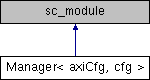

template<typename axiCfg, typename cfg>

class Manager< axiCfg, cfg >

An AXI manager that generates random traffic for use in a testbench.

- Template Parameters

-

| axiCfg | A valid AXI config. |

| cfg | A valid config for the manager (such as managerCfg). |

- Overview

- Manager is an AXI manager block for use in testbenches. It generates read and write requests and checks the responses. The block supports AXI configurations with and without burst mode, write strobes, and write responses. The block enforces the following via assertion:

- Manager may not issue a read to an address it has not yet written to.

- Read response data must match the most recent write data to the same address.

- Manager may not issue writes with no strobe bits asserted to an address and then read from that address.

- Responses should assert the AXI "OKAY" response code.

- The number of read (write) responses should not exceed the number of read (write) requests.

In addition, the block asserts a done signal only when each request has received a corresponding response. The Manager generates random requests according to the following algorithm:

- Writes are generated to an address randomly selected from the valid range. 20% of writes have burst length greater than one; these writes randomly select a burst length from the valid range. 20% of write data beats have nonuniform strobes; the strobe bits of these write data beats are randomly set. Some data bits are generated via a hash of the address, while others are randomly generated. The data associated with a given address is stored locally so reads to that address can be validated later.

- Every AXI address that is written to (including multiple addresses for bursts) is added to the list of valid read addresses, which is initially empty. If write responses are enabled, the addresses are added only when the write response is received; otherwise, they are added when the write is sent.

- If the readDelay is greater than zero, a delay elapses before addresses that have been written to are added to the list of valid read addresses. If a write is issued to an address that has been previously written to, the address is removed from the list of valid read addresses and the readDelay timer for that address is reset.

- Writes that are issued to an address that has an outstanding read request in flight are discarded and not issued. Reads that are issued to an address that has an outstanding write request in flight are not issued (unless write requests are not supported, in which case only a non-zero readDelay prevents this race).

- Reads are randomly selected from the list of valid read addresses, so that reads only issue to address that have already been written to. This means that no reads issue until the first write response has returned.

- 50% of reads requests are initiated as bursts, with the burst length randomly selected from the valid range. If a read burst would include one or more addresses as part of the burst that have not yet been written to, the read request is discarded and not issued.

Definition at line 87 of file Manager.h.